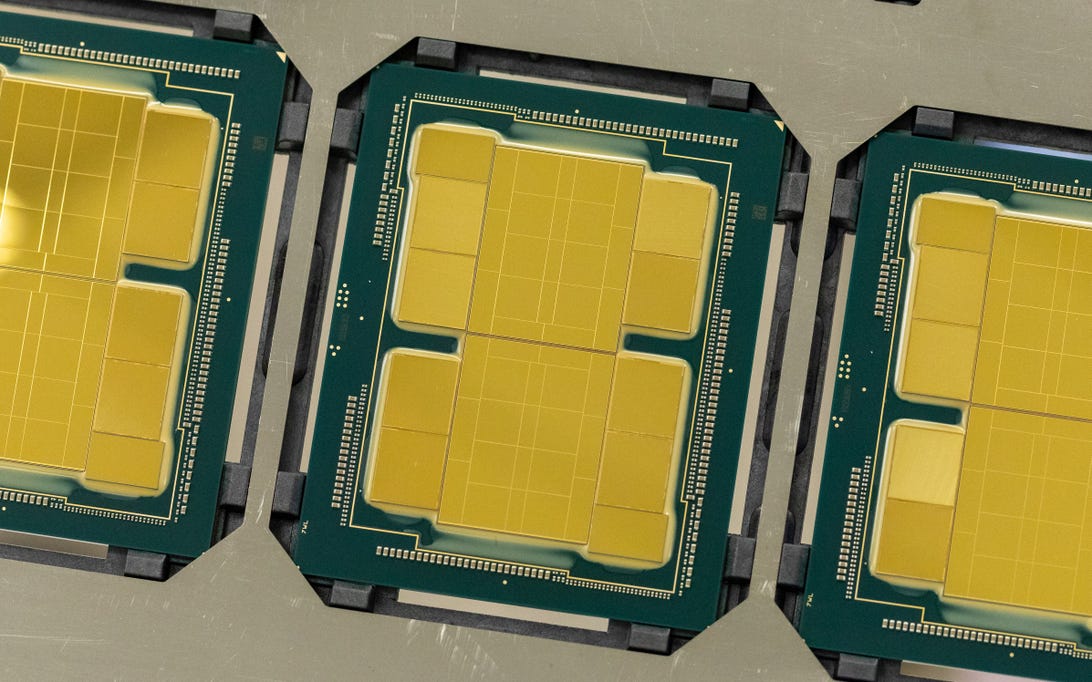

Intel programs a number of “chiplets” into one gargantuan Ponte Vecchio processor. The brand new UCIe alliance will have to make such packaging more straightforward.

Stephen Shankland/CNET

Nearly all the global’s greatest chipmakers have banded in combination so that you could show you how to bring together processor parts referred to as chiplets into one greater software. The hassle stands to assist stay Moore’s Legislation ticking, at the same time as engineering difficulties and prime prices impede growth in semiconductor production.

Contributors of the brand new Common Chiplet Interconnect Specific (UCIe) alliance, introduced Wednesday, come with chip producers Intel, Samsung and Taiwan Semiconductor Production Co. along side chip designers AMD, Arm, Google, Meta, Microsoft and Qualcomm.

Processors for years consisted of person rectangles, entire chips filled with circuitry. More and more, regardless that, chip designers and producers are assembling collections of chiplets into greater units. The theory, referred to as heterogeneous integration, shall we chipmakers reuse parts for years to decrease prices, make a selection amongst producers with other skills and spend money on probably the most complex production most effective the place it makes financial sense. That, in flip, will have to imply ever extra transistors — chips’ core processing era — for extra complex units.

“We predict the UCIe consortium to foster a colourful chiplet ecosystem,” Cheolmin Park, a vp in Samsung Electronics’ reminiscence trade and one among a number of executives who praised, stated the hassle in a commentary.

Probably the most conspicuous absences from the checklist are Nvidia and Apple, neither of which commented for this tale.

Probably the most excessive instance of this complex packaging is Intel’s Ponte Vecchio processor, which mixes separate chiplets for processing, graphics and reminiscence right into a mammoth software with greater than 100 billion transistors. Ponte Vecchio’s quantity crunching and AI prowess is designed for the Aurora supercomputer, however packaging is spreading to extra mainstream units like new AMD processors using the corporate’s 3-D V-Cache reminiscence packaging era.

The UCIe effort is designed to standardize verbal exchange hyperlinks amongst other chiplets, also known as die since they are diced from greater round silicon wafers. Preferably, that are supposed to decrease the limitations for all chip designers to make use of the manner.